## So far in memory management...

- Logical vs physical address

- MMU for translation

- Swapping: moving memory back and forth from storage

- Contiguous allocation

- Base and limit register for protection

- MMU supported

- External and internal fragmentation

### Paging for noncontiguous allocation

- Logical address space of a process can be noncontiguous; process is allocated physical memory whenever the latter is available

- Divide physical memory into fixed-sized blocks called frames (size is power of 2, between 512 bytes and 8192 bytes)

- Divide logical memory into blocks of same size called pages.

- Keep track of all free frames

- To run a program of size n pages, need to find n free frames and load program

- Set up a page table to translate logical to physical addresses

- ▶ This scheme will create internal fragmentation

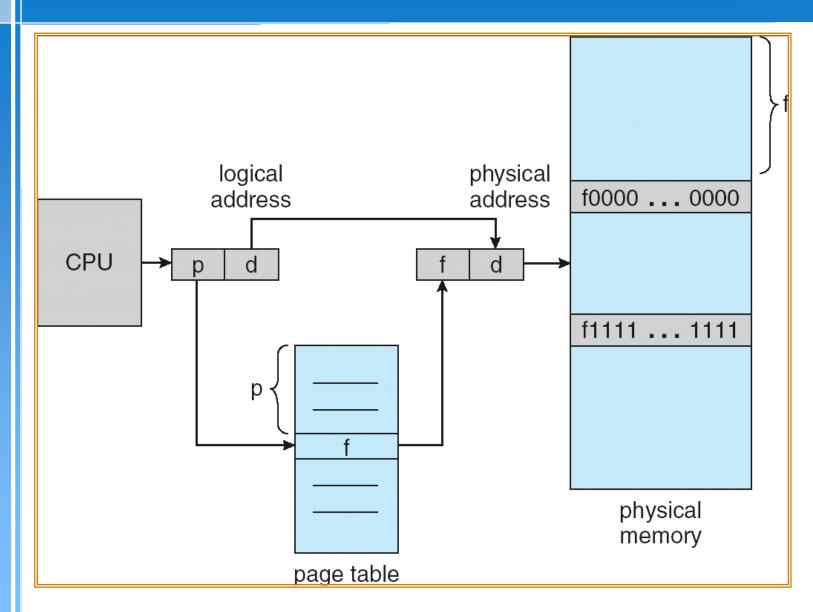

#### **Address Translation Scheme**

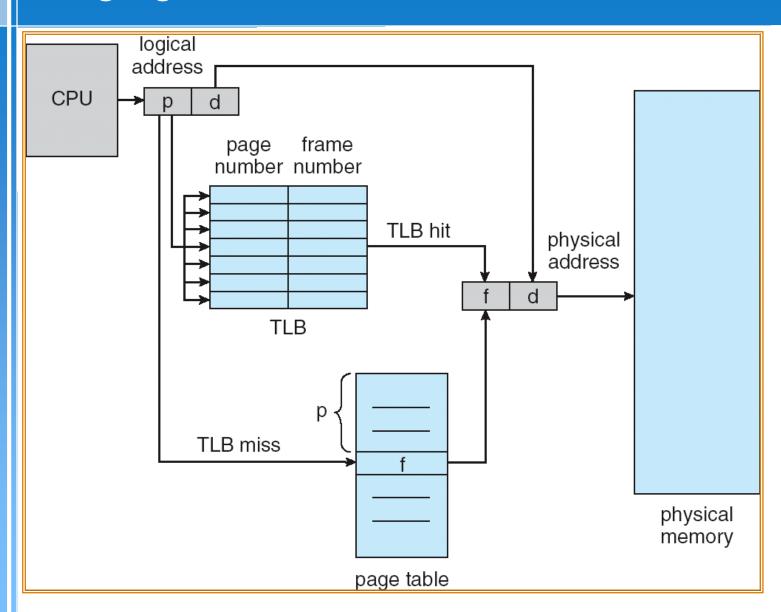

- ▶ Address generated by CPU is divided into:

- Page number (p) used as an index into a page table which contains base address of each page in physical memory

- Page offset (d) combined with base address to define the physical memory address that is sent to the memory unit

#### **Address Translation Architecture**

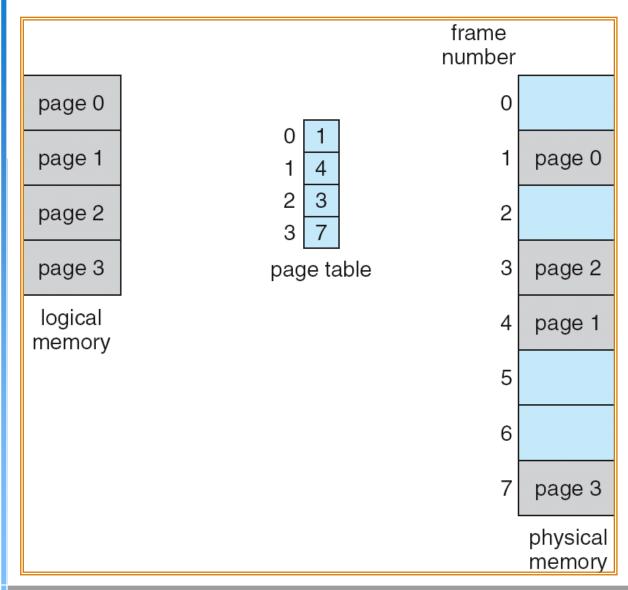

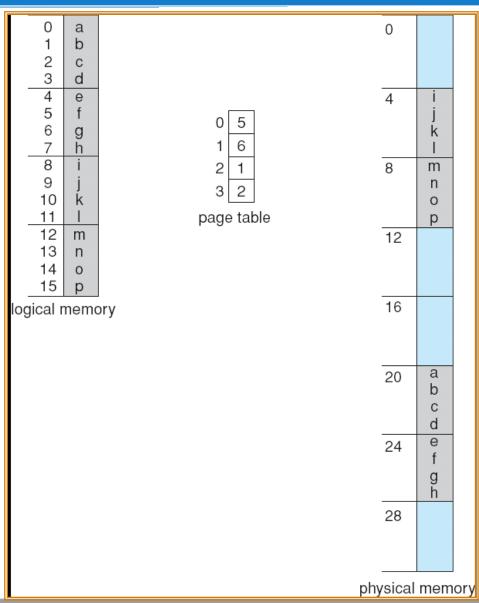

# Paging Example

# Paging Example

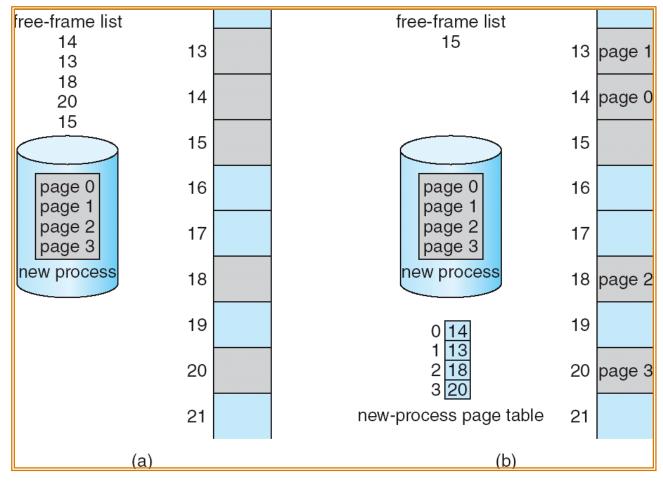

## Free Frames

Before allocation

After allocation

3/9/08

### Implementation of Page Table

- Page table is kept in main memory

- Page-table base register (PTBR) points to the page table

- Page-table length register (PRLR) indicates size of the page table

- In this scheme every data/instruction access requires two memory accesses. One for the page table and one for the data/instruction.

- The two memory access problem can be solved by the use of a special fast-lookup hardware cache called associative memory or translation lookaside buffers (TLBs)

## **Associative Memory**

Associative memory – parallel search

| Page # | Frame # |

|--------|---------|

|        |         |

|        |         |

|        |         |

|        |         |

Address translation (A', A'')

- If A´ is in associative register, get frame # out

- Otherwise get frame # from page table in memory

# Paging Hardware With TLB

#### **Effective Access Time**

- Associative Lookup =  $\varepsilon$  time unit

- Assume memory cycle time is 1 microsecond

- ▶ Hit ratio percentage of times that a page number is found in the associative registers; ratio related to number of associative registers

- $\blacktriangleright$  Hit ratio =  $\alpha$

- Effective Access Time (EAT)

EAT =

$$(1 + \varepsilon) \alpha + (2 + \varepsilon)(1 - \alpha)$$

=  $2 + \varepsilon - \alpha$